Efficient eye diagram testing in DDR3/DDR4 system designs

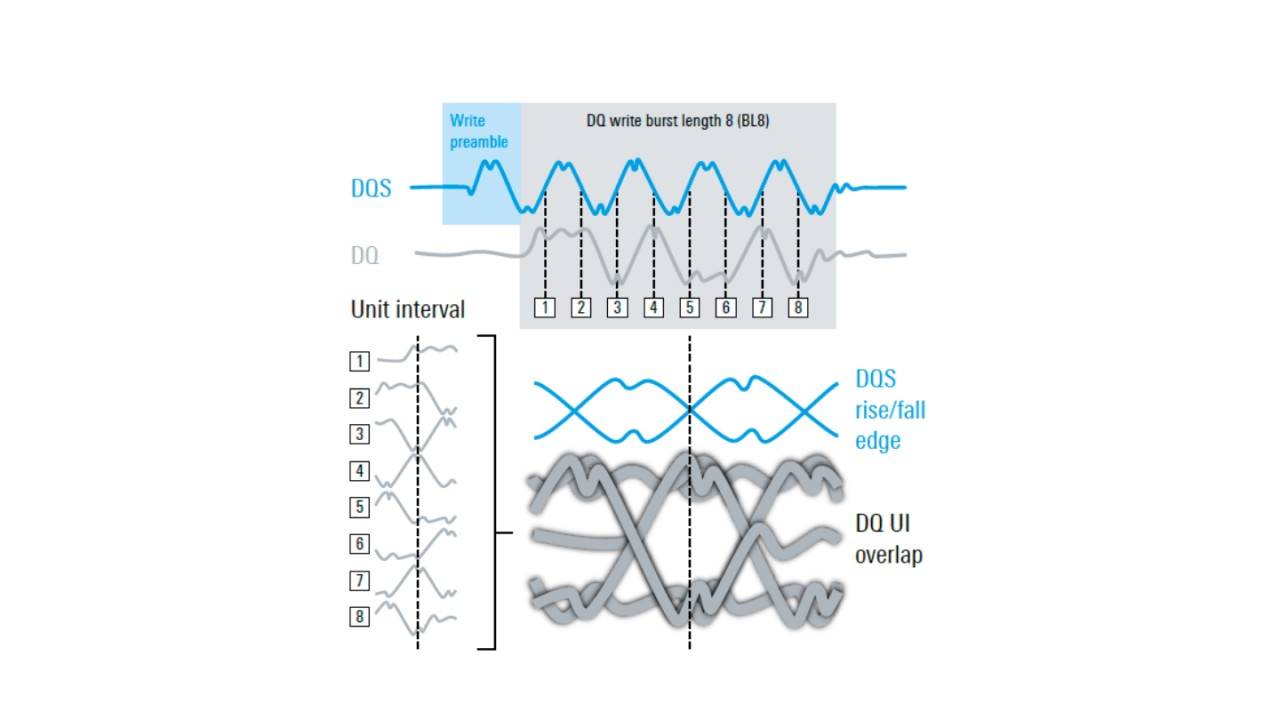

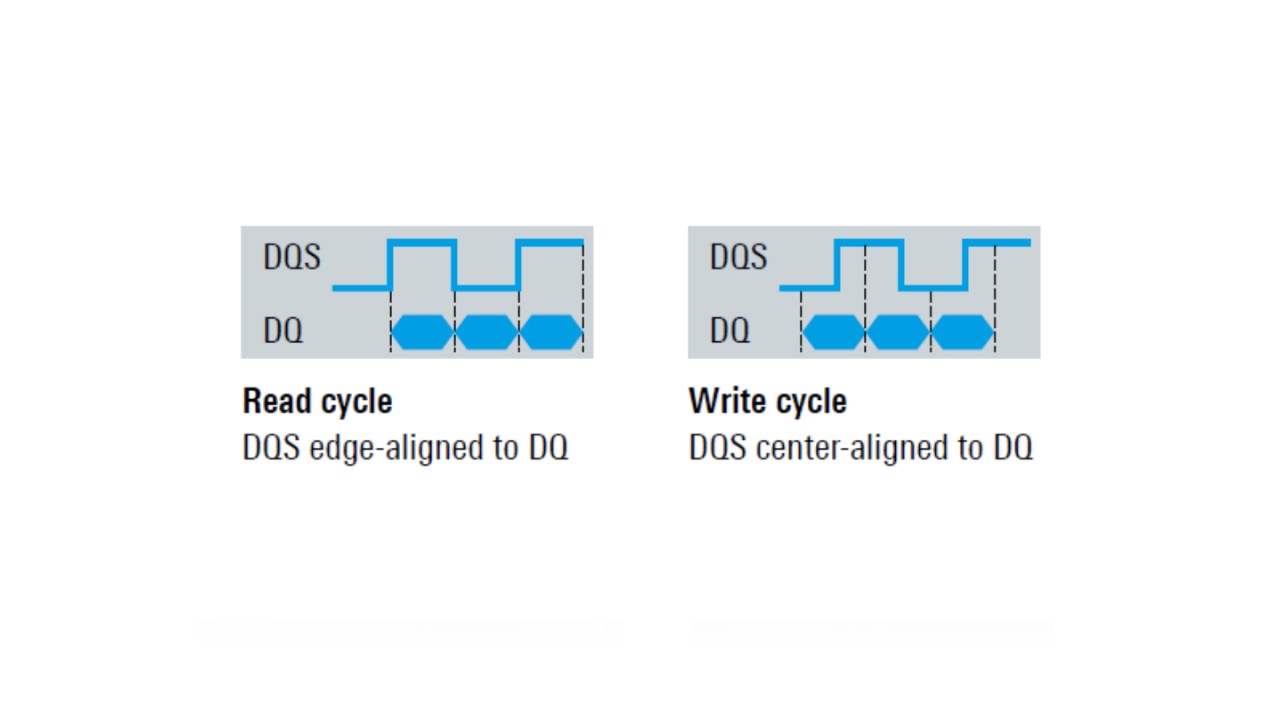

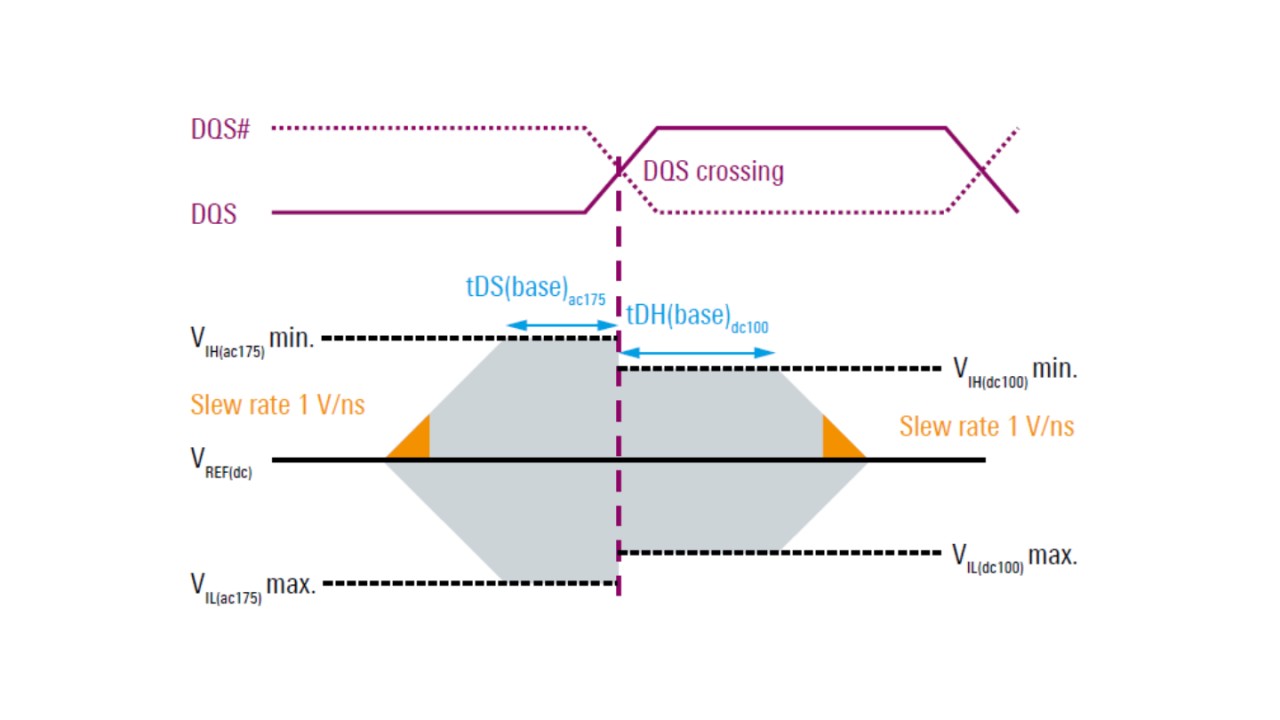

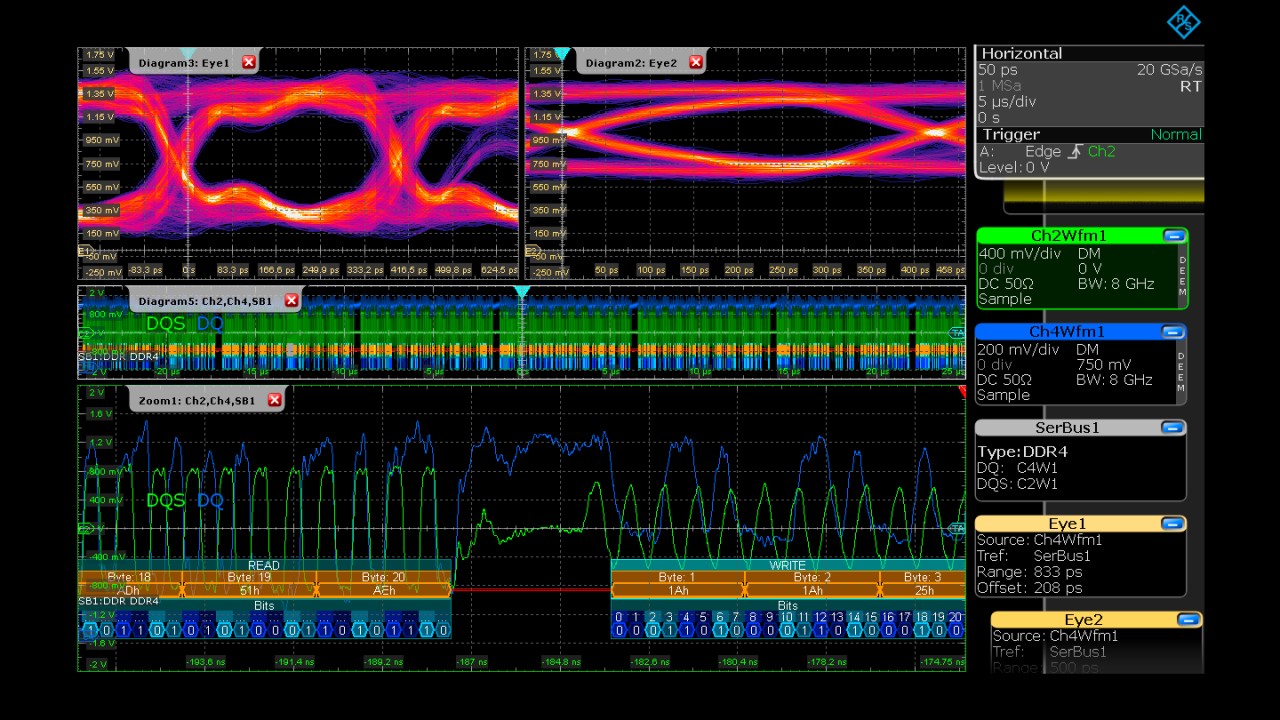

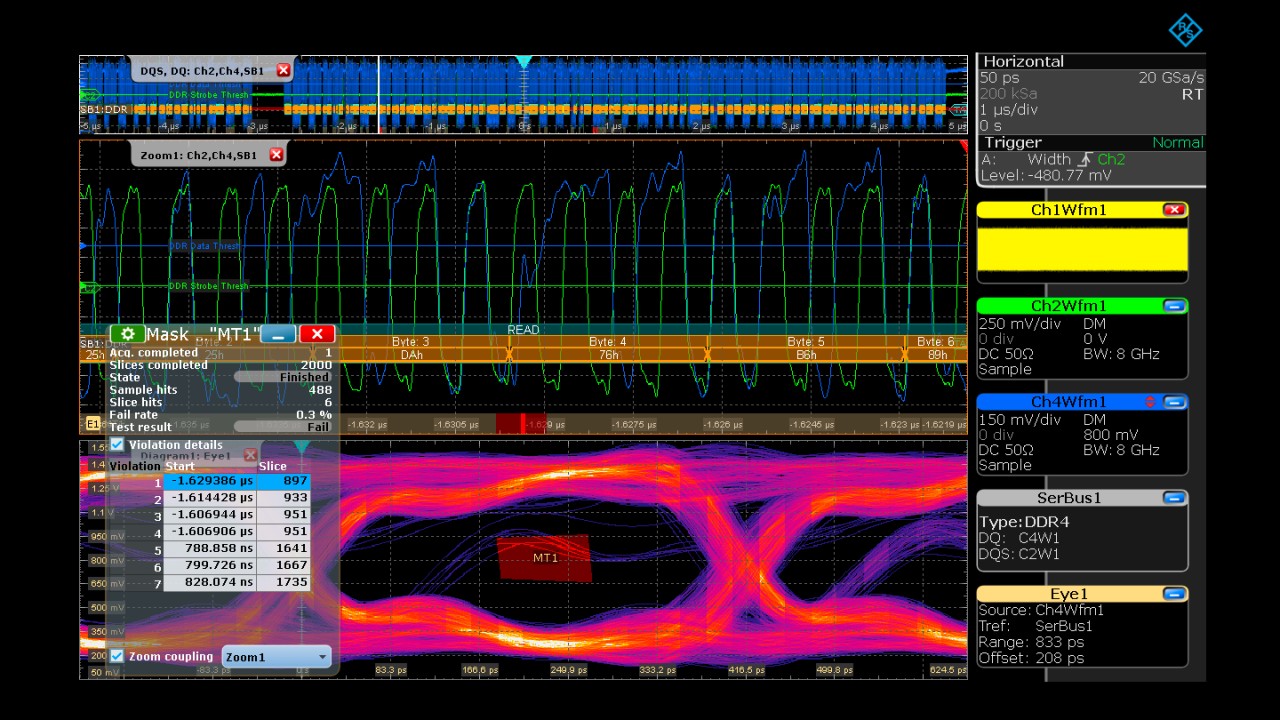

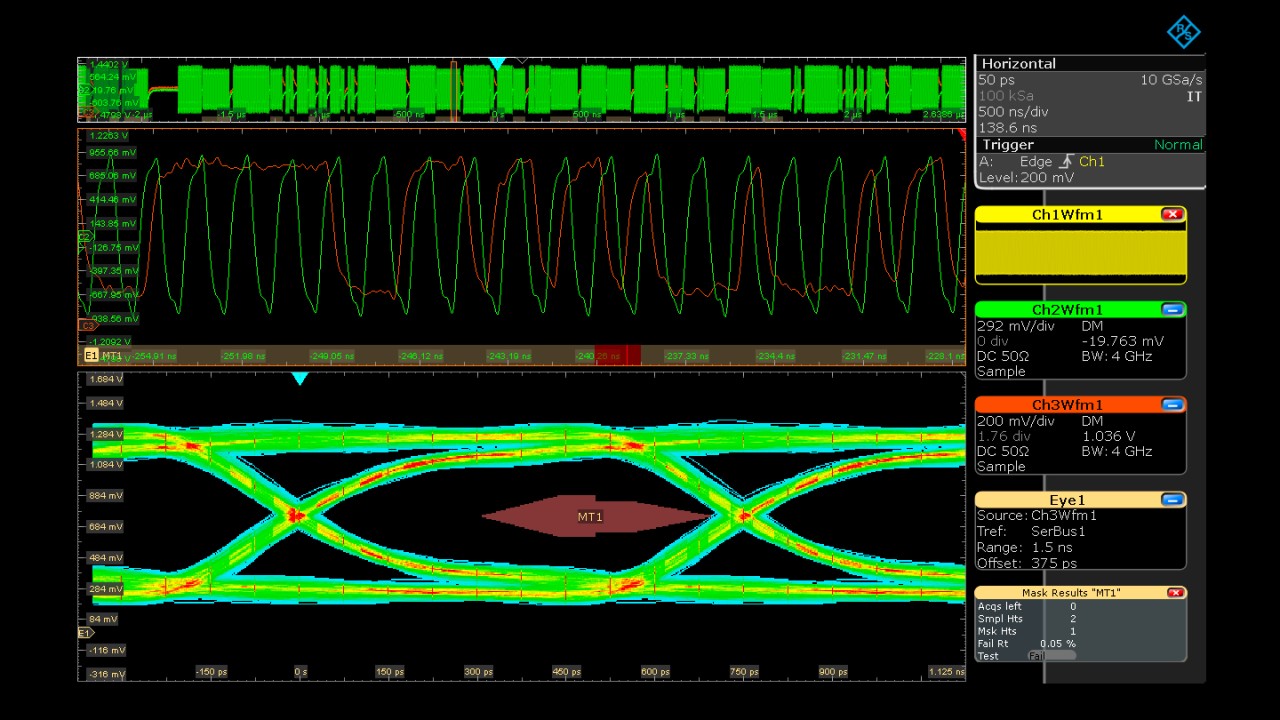

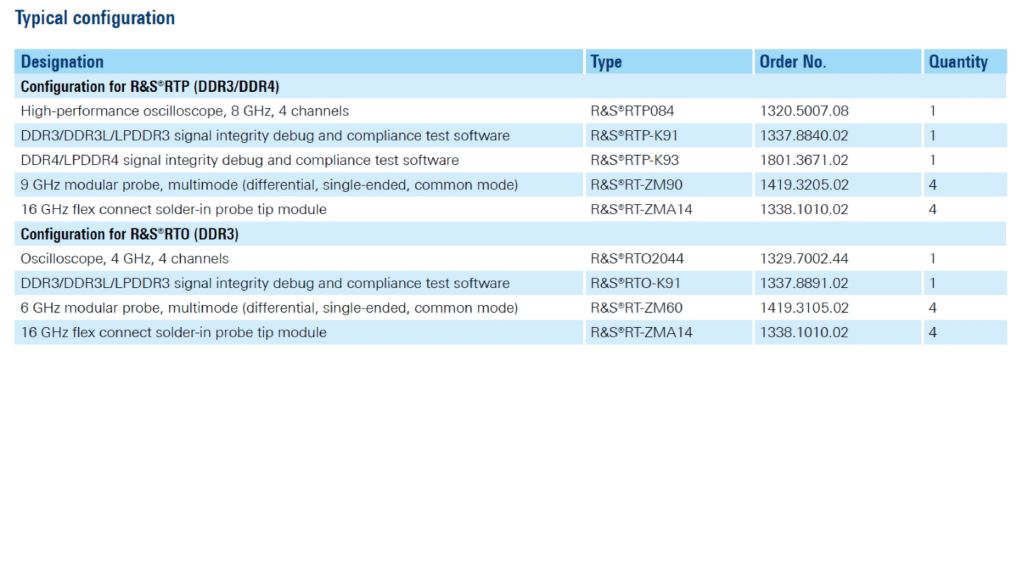

Compliance testing is essential to ensuring that dynamic random access memory (DRAM) signals meet the JEDEC specifications for parameters such as timing, slew rates and voltage levels. For system verification and debugging, eye diagram measurements are the most important tools for efficiently analyzing the signal integrity in any digital design. The specific nature of DDR requires a dedicated solution with a powerful read/write separation to get meaningful eye diagrams on the DDR data bus.