Your task

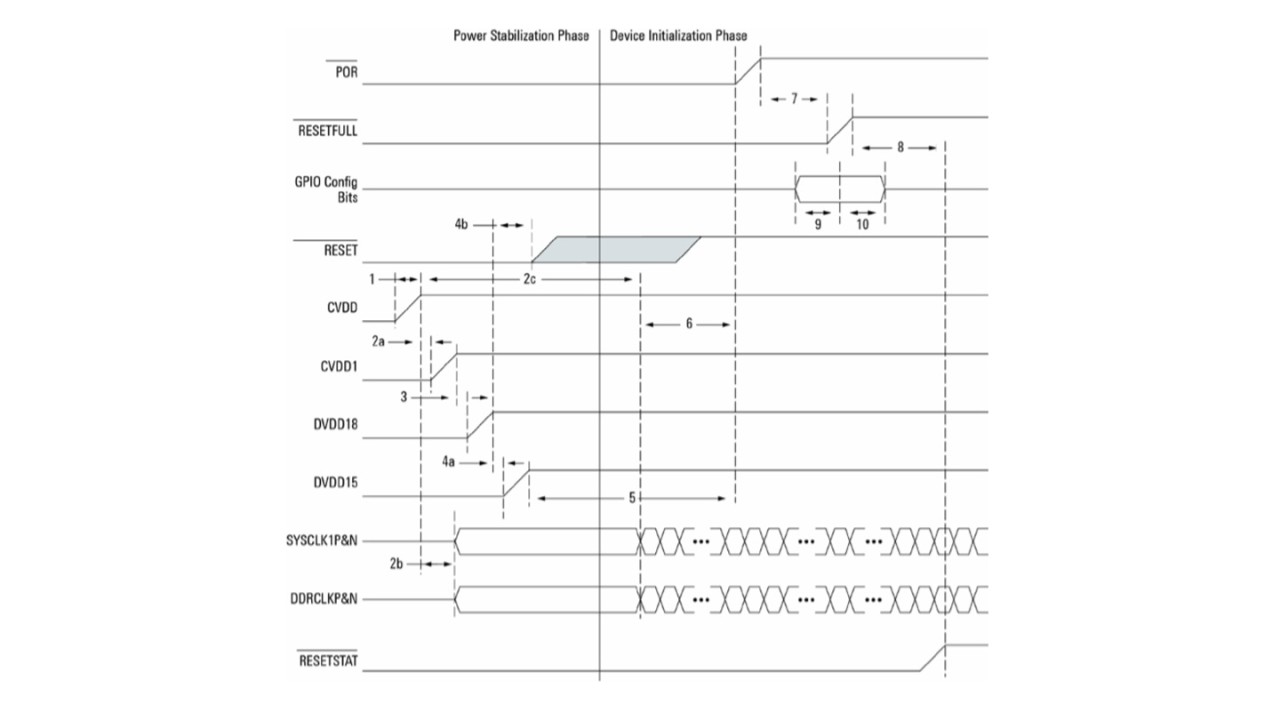

When powering up complex electronic components like FPGAs or CPUs, several supply voltages need to be applied in a specific order and with certain delay or ramp-up times. It is necessary to minimize current draw and ensure that the I/Os are in a high-impedance state at power-up.

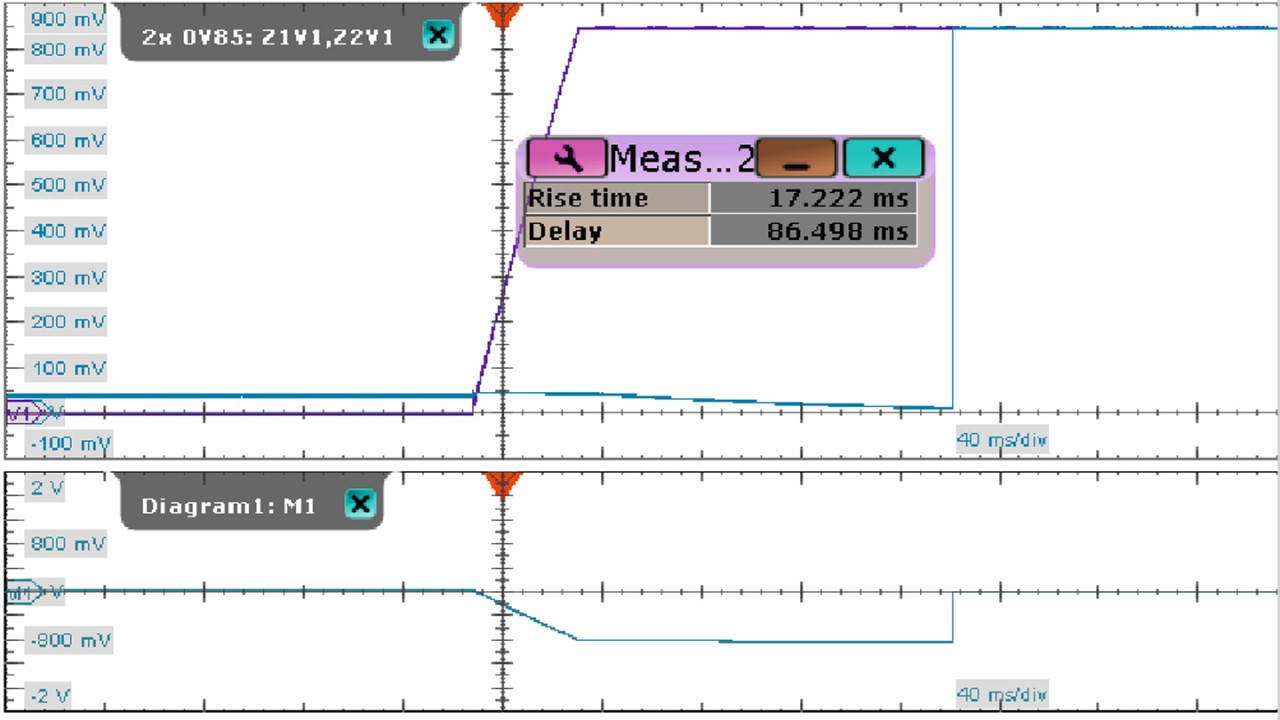

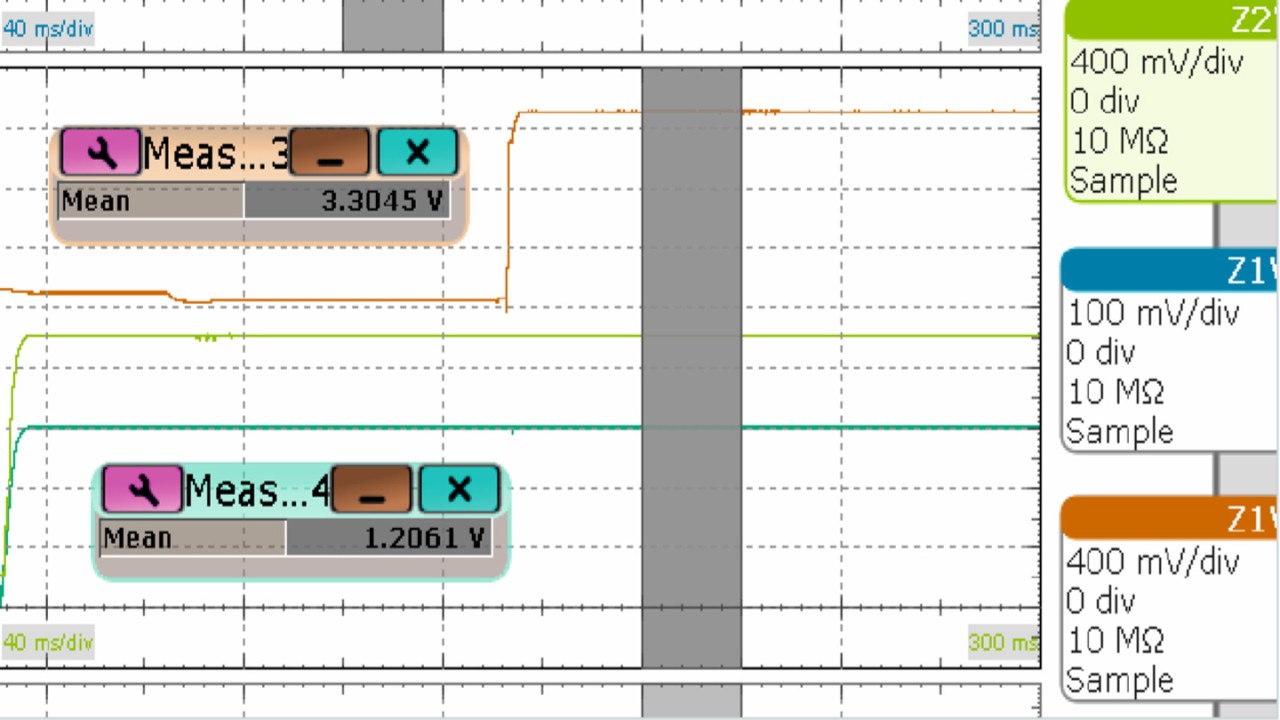

The recommended power-down sequence is usually the reverse of the power-up sequence. If these sequences are not followed, the current can exceed the specified limits which may lead to the component malfunctioning or being damaged. During circuit design, it is important to capture and analyze the characteristics of several voltages during startup and shutdown, as well as power breakdown.